קטגורית מוצרים

תגיות מוצרים

אתרי Fmuser

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> אפריקאית

- sq.fmuser.net -> אלבנית

- ar.fmuser.net -> ערבית

- hy.fmuser.net -> ארמנית

- az.fmuser.net -> אזרבייג'נית

- eu.fmuser.net -> באסקית

- be.fmuser.net -> בלארוסית

- bg.fmuser.net -> בולגרית

- ca.fmuser.net -> קטלאנית

- zh-CN.fmuser.net -> סינית (פשוטה)

- zh-TW.fmuser.net -> סינית (מסורתית)

- hr.fmuser.net -> קרואטית

- cs.fmuser.net -> צ'כית

- da.fmuser.net -> דנית

- nl.fmuser.net -> הולנדית

- et.fmuser.net -> אסטונית

- tl.fmuser.net -> פיליפינית

- fi.fmuser.net -> פינית

- fr.fmuser.net -> צרפתית

- gl.fmuser.net -> גליציאנית

- ka.fmuser.net -> גרוזינית

- de.fmuser.net -> גרמנית

- el.fmuser.net -> יוונית

- ht.fmuser.net -> קריאולית האיטי

- iw.fmuser.net -> עברית

- hi.fmuser.net -> הינדית

- hu.fmuser.net -> הונגרית

- is.fmuser.net -> איסלנדית

- id.fmuser.net -> אינדונזית

- ga.fmuser.net -> אירית

- it.fmuser.net -> איטלקית

- ja.fmuser.net -> יפנית

- ko.fmuser.net -> קוריאנית

- lv.fmuser.net -> לטבית

- lt.fmuser.net -> ליטאי

- mk.fmuser.net -> מקדונית

- ms.fmuser.net -> מלאית

- mt.fmuser.net -> מלטזית

- no.fmuser.net -> נורווגית

- fa.fmuser.net -> פרסית

- pl.fmuser.net -> פולני

- pt.fmuser.net -> פורטוגזית

- ro.fmuser.net -> רומנית

- ru.fmuser.net -> רוסית

- sr.fmuser.net -> סרבית

- sk.fmuser.net -> סלובקית

- sl.fmuser.net -> סלובנית

- es.fmuser.net -> ספרדית

- sw.fmuser.net -> סווהילי

- sv.fmuser.net -> שוודית

- th.fmuser.net -> תאילנדי

- tr.fmuser.net -> טורקית

- uk.fmuser.net -> אוקראינית

- ur.fmuser.net -> אורדו

- vi.fmuser.net -> וייטנאמי

- cy.fmuser.net -> וולשית

- yi.fmuser.net -> יידיש

מהו חצי עדף: תרשים מעגלים ויישומיו

Date:2021/10/18 21:55:58 Hits:

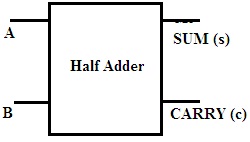

Half Adder הוא מסוג מעגלים דיגיטליים בסיסיים. מוקדם יותר ישנן פעולות שונות המבוצעות במעגלים אנלוגיים. לאחר גילוי האלקטרוניקה הדיגיטלית, מבוצעות בו פעולות דומות. המערכות הדיגיטליות נחשבות ליעילות ואמינות. בין הפעולות השונות, אחת הפעולות הבולטות היא אריתמטיקה. הוא כולל חיבור, חיסור, כפל וחלוקה. עם זאת, כבר ידוע שמדובר במחשב, כל גאדג'ט אלקטרוני כמו מחשבון יכול לבצע פעולות מתמטיות. פעולות אלה מתבצעות מורכבות מערכים בינאריים. הדבר אפשרי על ידי נוכחות מעגלים מסוימים בו. מעגלים אלה מכונים תוספים וחוסכים בינאריים. מעגלים מסוג זה מיועדים לקודים הבינאריים, עודפי -3 קודים וקודים אחרים גם כן. מוסיפים בינארי נוספים מסווגים לשני סוגים. הם: Half Adder ו- Full Adder מהו Half Adder? מעגל אלקטרוני דיגיטלי המתפקד לביצוע התוספת במספרים הבינאריים מוגדר כחצי Adder. תהליך ההוספה הוא הכחשה ההבדל היחיד הוא מערכת המספרים שנבחרה. במערכת המספור הבינארית קיימים רק 0 ו -1. משקל המספר מבוסס לחלוטין על המיקומים של הספרות הבינאריות. בין אלה 1 ו -0, 1 מטופל כמספרה הגדולה ביותר ו -0 כאל הספרה הקטנה יותר. תרשים הבלוק של המפרסם הזה הוא חצי תרשים חצי תרשים מעגל עפר חצי אפרדר מורכב משתי כניסות ומייצר שתי יציאות. זה נחשב למעגלים הדיגיטליים הפשוטים ביותר. הכניסות למעגל זה הן הביטים שעליהם יש לבצע את התוספת. התפוקות המתקבלות הן הסכום והנשיאה.

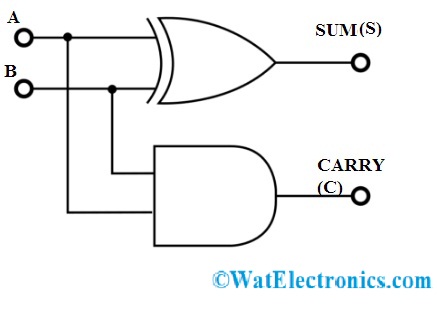

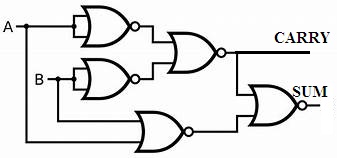

חצי תרשים חצי תרשים מעגל עפר חצי אפרדר מורכב משתי כניסות ומייצר שתי יציאות. זה נחשב למעגלים הדיגיטליים הפשוטים ביותר. הכניסות למעגל זה הן הביטים שעליהם יש לבצע את התוספת. התפוקות המתקבלות הן הסכום והנשיאה.  חצי אדוור המעגל של עפיסה זו מורכב משני שערים. הם שערי AND ו- XOR. התשומות המיושמות זהות לשני השערים הקיימים במעגל. אבל הפלט נלקח מכל שער. הפלט של שער ה- XOR מכונה SUM והפלט של AND ידוע CARRY.Talder Adder Truth Half Adder כדי לקבל את היחס בין הפלט המתקבל לקלט המיושם ניתן לנתח באמצעות טבלה המכונה טבלת אמת.

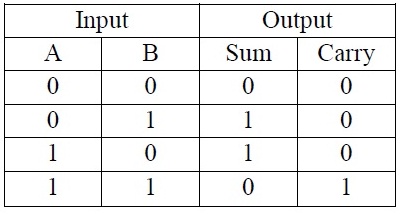

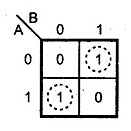

חצי אדוור המעגל של עפיסה זו מורכב משני שערים. הם שערי AND ו- XOR. התשומות המיושמות זהות לשני השערים הקיימים במעגל. אבל הפלט נלקח מכל שער. הפלט של שער ה- XOR מכונה SUM והפלט של AND ידוע CARRY.Talder Adder Truth Half Adder כדי לקבל את היחס בין הפלט המתקבל לקלט המיושם ניתן לנתח באמצעות טבלה המכונה טבלת אמת. טבלת האמת של חצי עו"ד מלוח האמת לעיל הנקודות ניכרות כדלקמן: אם A = 0, B = 0 שהן שתי התשומות שהוחלו הן 0. ואז שתי הפלט SUM ו- CARRY הן 0. בין שתי תשומות מיושמות אם מישהו הקלט הוא 1 ואז SUM יהיה b e1 אבל CARRY הוא 0. אם שתי הקלטות הן 1 אז SUM יהיה שווה ל- 0 וה- CARRY יהיה שווה ל- 1. בהתבסס על התשומות שהוחלו מחצית המפרץ ממשיכה עם הפעולה ניתן להוסיף את המשוואה לסוג מעגלים זה על ידי מושגי סכום המוצרים (SOP) ומוצרי סכום (POS). המשוואה הבולאנית לסוג מעגלים זה קובעת את הקשר בין התשומות המיושמות לתפוקות המתקבלות. כדי לקבוע את המשוואה ציירות ה- k מפותחות על סמך ערכי טבלת האמת. הוא מורכב משתי משוואות מכיוון שמשתמשים בו שני שערי היגיון. מפת ה- k של ה- carry היא

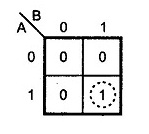

טבלת האמת של חצי עו"ד מלוח האמת לעיל הנקודות ניכרות כדלקמן: אם A = 0, B = 0 שהן שתי התשומות שהוחלו הן 0. ואז שתי הפלט SUM ו- CARRY הן 0. בין שתי תשומות מיושמות אם מישהו הקלט הוא 1 ואז SUM יהיה b e1 אבל CARRY הוא 0. אם שתי הקלטות הן 1 אז SUM יהיה שווה ל- 0 וה- CARRY יהיה שווה ל- 1. בהתבסס על התשומות שהוחלו מחצית המפרץ ממשיכה עם הפעולה ניתן להוסיף את המשוואה לסוג מעגלים זה על ידי מושגי סכום המוצרים (SOP) ומוצרי סכום (POS). המשוואה הבולאנית לסוג מעגלים זה קובעת את הקשר בין התשומות המיושמות לתפוקות המתקבלות. כדי לקבוע את המשוואה ציירות ה- k מפותחות על סמך ערכי טבלת האמת. הוא מורכב משתי משוואות מכיוון שמשתמשים בו שני שערי היגיון. מפת ה- k של ה- carry היא  K-Map AND Gate משוואת הפלט של CARRY מתקבלת משער AND.C = A.B הביטוי הבולאני עבור SUM מתממש על ידי טופס SOP. מכאן שמפת K ל- SUM היא

K-Map AND Gate משוואת הפלט של CARRY מתקבלת משער AND.C = A.B הביטוי הבולאני עבור SUM מתממש על ידי טופס SOP. מכאן שמפת K ל- SUM היא K-Map for Sum (XOR) המשוואה שנקבעה היא S = A⊕ B יישומים היישומים של adder בסיסי זה הם כדלקמן לביצוע תוספות על סיביות בינאריות היחידה האריתמטית והלוגיקה הקיימת במחשב מעדיפה את מעגל ה- adder. להיווצרות מעגל ה- Adder Full. מעגלי היגיון אלה מועדפים בעיצוב מחשבונים. לחישוב הכתובות והטבלאות עדיפים מעגלים אלה. במקום תוספת בלבד, מעגלים אלה מסוגלים לטפל ביישומים שונים במעגלים דיגיטליים. יתר על כן, זה הופך להיות הלב של האלקטרוניקה הדיגיטלית. קוד VHDL קוד VHDL עבור ספריית מעגל חצי הספינה ieee; השתמש ב- ieee.std_logic_1164.all; ישות half_adder isport (a, b: in bit; sum, carry: out bit); end half_adder ; נתוני ארכיטקטורה של half_adder isbeginsum <= a xor b; נושאים <= a ו- b; נתוני סיום; שאלות נפוצות 1. למה אתה מתכוון באדדר? המעגלים הדיגיטליים שמטרתם היחידה היא לבצע תוספת ידועים בשם Adders. אלה המרכיבים העיקריים של ALU. התוספים פועלים בנוסף לפורמטים השונים של מספרים. תפוקות התוספים הם הסכום והנשיאה .2. מהן המגבלות של חצי עדף? לא ניתן להוסיף את נקודת הנשיאה שנוצרה מהסיביה הקודמת היא המגבלה של המפרק הזה. כדי לבצע הוספה למספר סיביות לא ניתן להעדיף מעגלים אלה .3. כיצד ליישם חצי אפידר באמצעות NOR Gate? יישום סוג זה של אדרדר יכול להתבצע גם באמצעות שער NOR. זהו עוד שער אוניברסלי.

K-Map for Sum (XOR) המשוואה שנקבעה היא S = A⊕ B יישומים היישומים של adder בסיסי זה הם כדלקמן לביצוע תוספות על סיביות בינאריות היחידה האריתמטית והלוגיקה הקיימת במחשב מעדיפה את מעגל ה- adder. להיווצרות מעגל ה- Adder Full. מעגלי היגיון אלה מועדפים בעיצוב מחשבונים. לחישוב הכתובות והטבלאות עדיפים מעגלים אלה. במקום תוספת בלבד, מעגלים אלה מסוגלים לטפל ביישומים שונים במעגלים דיגיטליים. יתר על כן, זה הופך להיות הלב של האלקטרוניקה הדיגיטלית. קוד VHDL קוד VHDL עבור ספריית מעגל חצי הספינה ieee; השתמש ב- ieee.std_logic_1164.all; ישות half_adder isport (a, b: in bit; sum, carry: out bit); end half_adder ; נתוני ארכיטקטורה של half_adder isbeginsum <= a xor b; נושאים <= a ו- b; נתוני סיום; שאלות נפוצות 1. למה אתה מתכוון באדדר? המעגלים הדיגיטליים שמטרתם היחידה היא לבצע תוספת ידועים בשם Adders. אלה המרכיבים העיקריים של ALU. התוספים פועלים בנוסף לפורמטים השונים של מספרים. תפוקות התוספים הם הסכום והנשיאה .2. מהן המגבלות של חצי עדף? לא ניתן להוסיף את נקודת הנשיאה שנוצרה מהסיביה הקודמת היא המגבלה של המפרק הזה. כדי לבצע הוספה למספר סיביות לא ניתן להעדיף מעגלים אלה .3. כיצד ליישם חצי אפידר באמצעות NOR Gate? יישום סוג זה של אדרדר יכול להתבצע גם באמצעות שער NOR. זהו עוד שער אוניברסלי. חצי עוף באמצעות שערי NOR 4. כיצד ליישם חצי אפידר באמצעות שער NAND? שער NAND הוא אחד מסוגי השערים האוניברסליים. זה מציין כי כל סוג של עיצוב מעגלים אפשרי על ידי שימוש בשערי NAND.

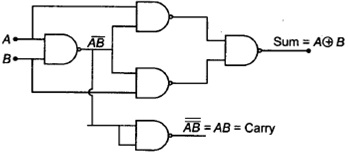

חצי עוף באמצעות שערי NOR 4. כיצד ליישם חצי אפידר באמצעות שער NAND? שער NAND הוא אחד מסוגי השערים האוניברסליים. זה מציין כי כל סוג של עיצוב מעגלים אפשרי על ידי שימוש בשערי NAND. חצי אדר מהמעגל הנ"ל ניתן לייצר את פלט הנשיאה על ידי החלת הפלט של שער NAND אחד על הקלט כשער NAND אחר. אין זה אלא מוכר לתפוקה המתקבלת משער AND. ניתן לייצר את משוואת הפלט של SUM על ידי החלת הפלט של שער NAND הראשוני יחד עם הכניסות הבודדות של A ו- B לשערי NAND נוספים. לבסוף, הפלט המתקבל על ידי אותם שערים NAND מוחל שוב על השער. מכאן שהפלט עבור SUM נוצר.לכן ניתן לעצב את האפנדר הבסיסי במעגל הדיגיטלי על ידי שימוש בשערי היגיון שונים. אבל התוספת מרובה הסיביות מסתבכת ונחשבת למגבלה של חצי הספיגה. האם תוכל לתאר באיזה IC משתמשים לפעולת התוספת בכל מונים מעשיים?

חצי אדר מהמעגל הנ"ל ניתן לייצר את פלט הנשיאה על ידי החלת הפלט של שער NAND אחד על הקלט כשער NAND אחר. אין זה אלא מוכר לתפוקה המתקבלת משער AND. ניתן לייצר את משוואת הפלט של SUM על ידי החלת הפלט של שער NAND הראשוני יחד עם הכניסות הבודדות של A ו- B לשערי NAND נוספים. לבסוף, הפלט המתקבל על ידי אותם שערים NAND מוחל שוב על השער. מכאן שהפלט עבור SUM נוצר.לכן ניתן לעצב את האפנדר הבסיסי במעגל הדיגיטלי על ידי שימוש בשערי היגיון שונים. אבל התוספת מרובה הסיביות מסתבכת ונחשבת למגבלה של חצי הספיגה. האם תוכל לתאר באיזה IC משתמשים לפעולת התוספת בכל מונים מעשיים?

השאר הודעה

רשימת הודעות

תגובות Loading ...